April 9, 2002

## **CPCI – PCI-X**

## **Analyzer & Exerciser**

- ◆ 100 MHz PCI-X Analyzer/66MHz Exerciser

- ♦ 66 MHz, 64 Bit CPCI Analyzer/Exerciser

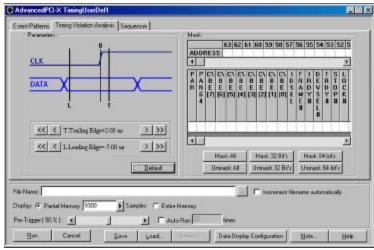

- ♦ 664 MHz Timing Analyzer

- Effective 10 GHz (100 Ps) setup & hold timing violations detector

- Comprehensive Statistical Analysis of Min & Max of over 100 parameters at user specific addresses

- ◆ 533 MBytes/Sec real-time continuous Performance Analysis & traffic generation

- Interactive "Linked" Exerciser 64 Bit, 66 MHz, 3.3 V/5V

- Automated PCI Device Compliance Test & Verification

- Ultimate GUI Interface optimized to enhance product development

- C-API for custom C program development

- FPGA design automatically upgrades the product features with each software update

### PCIBUS, TARGET SYSTEM

Analyze any PCI or PCI-X System Architecture running under any operating system.

#### HOST SOFTWARE

The TA700 software operates under Windows XP, 2000, NT SP 3.1 or higher, 98 or 95.

#### FIELD UPGRADABLE

FPGA based design allows automatic hardware upgrade to the latest added features each time a new version of the software is loaded.

The expansion slot is useful for systems with limited available PCI slots.

#### AUTOMATIC SYSTEM CLOCK DETECTION

The TA700C automatically detects and reports the system clock frequency.

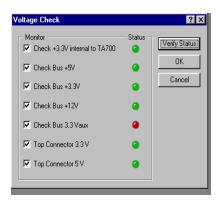

#### **VOLTAGE CHECK**

You may enable the TA700C to monitor the system voltages for a drop exceeding 5% of nominal and to flag this by illuminating a red LED. DUT voltages are not monitored by the TA700C.

### **Easy Mode** (Pre-Defined) Pre-Defined Setups allow Instant Debug & Analysis of Hardware and Software Problems

**"Capture Data & Trigger**" mode allows hardware or software oriented PCI bus debug, without requiring any programming or setup of the analyzer. A comprehensive selection of Pre -Defined setups allows capturing data on variety of trigger selections.

In addition to the pre-defined setups for data capture and trigger of bus cycles there are also several selections available for performance analysis, statistical analysis and TA700C as a bus Master to read and write variety of target registers and memory contents.

Capture Data & Trigger menu allows users to easily select capturing everything or to exclude Idles, Waits and Retries and/or to capture data at a specific address range. At the same time the user may also specify the trigger point from variety of available selections.

| Data Caphze Selection                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G Everything<br>C Specific Adheor(ex)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Exclude<br>T Idea T I I T T T T                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Tigge Point Selection                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Trigger On :                                         | Addess 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Address                                              | Command Cotto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Address<br>Any Internal                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bust Longer than new times                           | Door A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Burst Shorter than rmn times<br>Burst Transfers(DMA) | territoria de la companya |

| Data At Address<br>GNTs                              | ess/Data See: 19 12 84 C 64 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Marter Abot                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Occurrence of SERR# or PERR#<br>Protocol Enor        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| REGR                                                 | The Manage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                      | 2 C Ado But Stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

There are several selections available for triggering on an occurrence of a single signal to triggering on events causing system crashes

#### LIST OF PRE-DEFINED PROJECTS FOR "DATA CAPTURE & TRIGGER" MODE

- Trigger on specified address.

- Trigger on any interrupt.

- Trigger on burst longer than nnn times.

# **TA700C**

- Trigger on burst shorter than nnn times.

- Trigger when data burst is transferred.

- Trigger on specified data at address.

- Trigger when GNT# is asserted.

- Trigger when master abort occurs.

- Trigger on SERR# or PERR#.

- Trigger when a PCI protocol error is detected.

- Trigger when REQ# is asserted.

- Trigger when reset is de-asserted at rising edge of reset.

- Trigger when signal xxx is asserted and then de-asserted nnn times.

- Trigger when signal xxx asserted for more than nnn times.

- Trigger when signal xxx de-asserted for more than nnn times.

- Trigger when signal xxx deasserted for more than nnn times.

- Trigger when signal xxx is shorter than nnn times.

- Trigger on a target abort.

- Trigger on a target disconnect.

- Trigger on a target Retry.

- Trigger when a consecutive target Retry occurs more than nnn times.

- Trigger on target termination, combination.

- Trigger on Vendor ID and Device ID.

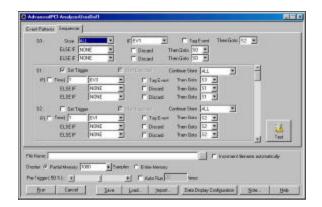

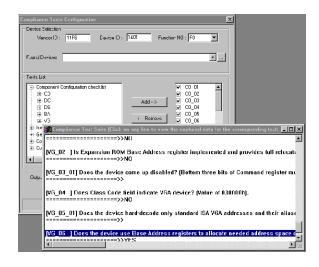

### Advanced Mode (User Setup) For Debugging of more Complex Problems

Users may define up to eight events covering all PCI bus signals for data/address capture or triggering. In addition the external signals may also be defined in the event menu for a condition on jump or trigger.

Up to 32 level state may be defined in the Sequencer. At each state the user may define what to capture and where to jump depending on occurrences of the events and/or their Boolean expression, protocol errors, timing errors, external signals and delay in time. Unlimited Else If and jumps may be defined in the Sequencer menu.

The advanced mode requires Event, Sequencer and Program files (for the exerciser mode) to be defined by the user.

Some examples of the Events and Sequencer features are indicated below.

| Kane           | JFER   | A0( )                                   | CBELL      | PAR | 10566 | FRAMES | 1 PDY | DEVOLU   | I STOPPE | しのに利用 | 8.4    | DATX   | と四月        | 地名丁香 | PMER | EXT<br>ETH<br>SIG<br>NAL |

|----------------|--------|-----------------------------------------|------------|-----|-------|--------|-------|----------|----------|-------|--------|--------|------------|------|------|--------------------------|

| EVI            |        | *******                                 | ******     | ×   | ×     | ×      | ×     | <b>.</b> | x x      | ×     | 10000  | XOOOK  | x          | 23   | κx   | 1000                     |

| EV2            |        | 200000000000000000000000000000000000000 | >000000000 | ×   | ×     | ×      | ×     | ×        | ĸж       | ×     | >00000 | X000K  | 300        | ×    | < X  | >000                     |

| EA3            |        | 100000000000000000                      | 300000000  |     |       | н      | н.    | X.       | ĸж       | X     | 30000  | 30000  | 300        | 80   | < H  | 3000                     |

| EVA            |        | >00000000000000000                      | 300000000  | XX  | 28    | ж      | ж     | X        | КΧ       | X     | >00000 | 3000K  | 305        | ж1   | K H  | 3000                     |

| EVE            |        | 20000000000000000                       | 300000000  | 300 | 3     | ×      | 20    | ×        | хх       |       |        | 30000  |            |      |      |                          |

| EVE            |        |                                         |            |     | 3     | х      | 2     | X.       | X X      |       |        |        |            |      |      |                          |

| EV7            | 1      | 10000000000000000                       | >000000000 |     |       |        |       |          | КЖ       |       |        | 100004 |            |      |      |                          |

| EVI            | ++++++ | x0000000000000000                       | >000000000 | ~~  | ×     | ×      | ×     | ×        | ×ж       | ×     | >0000  | 200000 | <b>X</b> X | X    | ¢Χ   | >000                     |

| Address Frange |        | 32.84 0 64.841                          |            |     |       |        |       |          |          |       |        |        |            | 24   | a da | Events                   |

The user defined menu also allows users to specify the output file name, pre-trigger value, number of data to be captured, notes about the setup by the user and execution of the program from the menu.

The Sequencer may be programmed using either, an intuitive GUI or a convenient textual programming window.

Sequencer, Menu style

| B Starte ( White Capturing AI PCI Signab AI "Every, Chedr ( If "EVI-Occuss", "This GOTO "Status" Otherwise Containe With This State ) B State ) Set, Trager Wide Capturing AI PCI Signals As "Every, Chedr (  | Add Dia<br>Add Dia<br>Room                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H"1"2KT Occurr - "Tan COTO "Sale?" Otherwise Costane With The Store )  See State2 ( White Cophering Ad PCI Egrads As "Every_Check" ( If "1"EVI" Occurs - "Tan OOTO "Inte?" Otherwise Contace With The Store 1 | Here and the second sec |

| Ne Name Contraction of State Manage Party State Manage Per Tagger (50.5) 1 1 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                | went lievane automaticaly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Sequencer, Text style

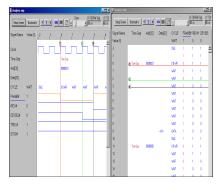

#### **DISPLAY CAPABILITY**

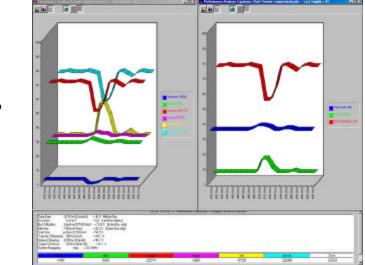

• List or Waveform captured data displayed individually or simultaneously.

- Ability to add/remove and rearrange captured signals by dragging signal names in the display windows.

- Display the value of X or Y cursor position.

- User defined color for each signal.

- Indicating "Time Gap" for when data discontinuity exist.

- User defined "Bookmark".

- Graphical display of latency time.

- Three waveform display cursors with their relative positions expressed as time or clocks.

- Cursors linked between waveform and list windows.

- Waveform display zoom from 0.1 to 10 about X, Y or around X and Y cursors.

- Jump relative to Trigger, X, Y Cursor or start within waveform display

- Any of PCI signals may be added or removed from the screen

#### EXTERNAL SIGNALS

16 external signals may be used for data capture, triggering or input to performance analysis.

| External Signal Names | ×                  |

|-----------------------|--------------------|

| -XGRP0                | -XGRP2             |

| XX00: EXTERNAL        | ∞08: ∞08           |

| ××01 : ××01           | ∞09: ∞09           |

| ×02: ×02              | ××10: ××10         |

| ∞03: ∞03              | ×11: ×11           |

|                       |                    |

| CXGRP1                | -XGRP3             |

| ××04: ××04            | XX12: XX12         |

| ××05: ××05            | XX13: XX13         |

| ₩06: ₩06              | ××14: ××14         |

| ××07: ××07            | XX15: XX15         |

|                       |                    |

| ОКСС                  | ancel <u>H</u> elp |

You may assign your own signal names for easy identification in captured signal displays.

#### **EXTERNAL TRIGGERS**

#### **OUTPUT TRIGGER**

A positive or negative level may be set for the external trigger output, external trigger will get set when trigger occurs in the sequencer.

| External Trigger |        |   |            | × |

|------------------|--------|---|------------|---|

| Output Trigger   | (J7)   |   |            |   |

| Negatir          | vel    | 0 | + Positive |   |

| OK               | Cancel | 1 | Help       |   |

## **TA700C**

#### **REVIEW AND EDIT FILES IN OTHER FORMATS**

Output files may be converted to **ASCII** text or **EXCEL**<sup>™</sup> spreadsheets for use in off-line data analysis programs. Also available from the tools menu is a graphical screen capture to a \*.**PCX** file format.

#### **POST PROCESSING UTILITIES**

#### SEARCH UTILITY

The search utility offers you the capability to:

- Search for any pattern.

- Search for consecutively recurring patterns.

- Search forward or backward.

- Search for patterns with user defined mnemonics.

#### **COMPARE UTILITY**

Allows the comparison of two captured files, entire file or partial.

#### DATA FILTERING

You may filter captured data files to include or exclude data patterns defined in mnemonics.

#### **MNEMONICS**

Up to 100 mnemonics may be assigned to 100 different patterns and saved as a file. An unlimited number of mnemonic files may be designed for use in various applications.

Mnemonics may be used to:

- Distinguish certain patterns in the display by name.

- Filter a pattern in or out of a data file.

- Search for patterns by name.

#### **PROTOCOL ERRORS PCI**

Per PCI Rev 2.1 & 2.2

The TA700C monitors and captures several different protocol errors automatically whenever a data capture occurs. You may enable all or any of the protocol errors to initiate the trigger by using a Protocol Error mask, when setting the sequencer to trigger on the Protocol Error or using the protocol Error selection from the "Trigger On" menu.

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | an a relact role and pro-                                                                               | control to a site to see a site                              |               |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------|

|                                                                                                                             | usual adults Michaelts h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |                                                              |               |

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         | easted PORe 22-041                                           |               |

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         | el entertector Porv 2324                                     | a –           |

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         | amelot POPer 21 551                                          |               |

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         | an owned after FRIMEIT room<br>control 3.31 Privat Francisco |               |

| 0.001-0018 ees and                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         | COMPANY AND COMPANY                                          |               |

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         |                                                              |               |

| Intel May PRIVE and                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                         | · Personei deischen we                                       | combined or 1 |

| ONE PETERS and                                                                                                              | enoted PEVE or Phile<br>tricking for second of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C # sens changed befor<br>beto photo of a Duel Ad                                                       | e Recornet deischem ver<br>dem Carle 1107 Mild als           |               |

| (1973). PENE van soort<br>(1972). PENE van soo                                                                              | enerted, PEVR pr7544<br>tricking for exampled<br>tind damp specialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Cill vers changed belo<br>tena photo of a Duel Ad<br>POTRes 21 - 2012                                   |                                                              |               |

| (1993) PEVE on som<br>(1993) PENE om som<br>(1993) PENE om som                                                              | enerted, PEY'N or Phile<br>sticking the on and of<br>stick dama possibly of<br>stud dama states of or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C4 see charget betw<br>tere photo of a Dash Ad<br>(RD/Rev 2.1 - 1282)<br>a PD Rev 2.1 - 225             |                                                              |               |

| CARD INTY'S new served<br>CARDO, PENET was not<br>CARDO, PENET year and<br>CARDO, PENET year and<br>CARDO, PENET year and   | enormal (PEVE or Phile<br>Initiality The animal ad-<br>nied during speciality of<br>rhad during sublisher age<br>(contrast of the second second second<br>second second second second second<br>second second second second second second<br>second second second second second<br>second second second second second<br>second second second second second second second<br>second second second second second second second second<br>second second second second second second second second<br>second second second second second second second second second second<br>second second second<br>second second second<br>second second sec | CR was charged before<br>lens phote of a Dud Ad<br>(PDRes 21 - 2013)<br>a PDRes 21 - 225<br>Resid (PDR) |                                                              |               |

| CARD ACT A sea sent<br>CARD) PORT may and<br>CARD) PORT and and<br>CARD PORT action<br>CARD PORT action<br>CARD PORT Action | enormal (PEVE or Phile<br>Initiality The animal ad-<br>nied during speciality of<br>rhad during sublisher age<br>(contrast of the second second second<br>second second second second second<br>second second second second second second<br>second second second second second<br>second second second second second<br>second second second second second second second<br>second second second second second second second second<br>second second second second second second second second<br>second second second second second second second second second second<br>second second second<br>second second second<br>second second sec | CR was charged before<br>lens phote of a Dud Ad<br>(PDRes 21 - 2013)<br>a PDRes 21 - 225<br>Resid (PDR) |                                                              |               |