# M8040A High-Performance BERT 64 Gbaud

Version 10.2

Master your next design

## **Table of Contents**

| Introduction                                                                                                                                                                                 | 3    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| M8000 Series of BER Test solutions                                                                                                                                                           | 5    |

| M8040A High-performance BERT 64 Gbaud                                                                                                                                                        | 5    |

| Repeatable and Accurate Results with M8040A                                                                                                                                                  | 7    |

| Emulate Stress Conditions for NRZ, PAM3 and PAM4 Input Tolerance Testing with M8040A                                                                                                         | 8    |

| Master PAM4 Receiver Test Challenges with M8040A                                                                                                                                             | 9    |

| Real-time Error Analysis for PAM4 and NRZ Signals                                                                                                                                            | 9    |

| Automated Receiver Calibration and Characterization for IEE 802.3bs/cd, IEEE 802.3ck, OIF-CEI-56G-VSR/-MR/-LR-PAM4, PCI Express 4.0, 5.0 and 6.0, USB 3.2, USB4 and TBT3 and TBT4 Interfaces |      |

| Specifications for M8045A and M8046A Modules and M8057A/B Remote Head                                                                                                                        | . 12 |

| Specifications for Pattern Generator Module M8045A and Remote Head M8057A/B                                                                                                                  | . 13 |

| Reference clock input (REF CLK IN)                                                                                                                                                           | . 19 |

| Jitter Specifications                                                                                                                                                                        | . 23 |

| External level interference (RI/SI) sources                                                                                                                                                  | . 27 |

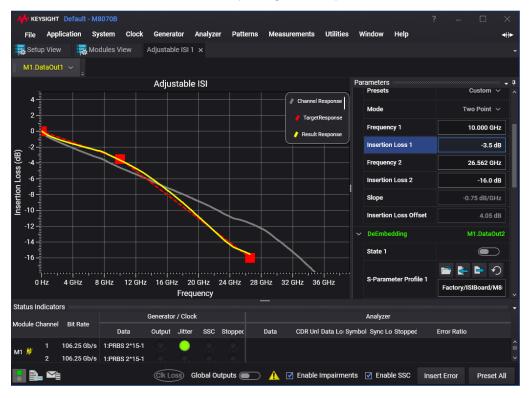

| Emulate ISI (inter-symbol interference) with M8049A                                                                                                                                          | . 29 |

| Pattern Sequencer, filler Symbol Filtering, and Interactive Link Training                                                                                                                    | . 30 |

| Interactive link training for PCIe                                                                                                                                                           | . 33 |

| Interactive link training for USB 3.2                                                                                                                                                        | . 34 |

| Specifications Analyzer Module (Error Detector) M8046A                                                                                                                                       | . 34 |

| Error Analysis of PAM4 Signals Using an UXR-Series                                                                                                                                           | . 42 |

| User Interface and Remote Control                                                                                                                                                            | . 44 |

| General characteristics and Physical Dimensions                                                                                                                                              | . 47 |

| Remote head M8057A/B                                                                                                                                                                         | . 48 |

| Specifications Assumptions                                                                                                                                                                   | . 48 |

| Ordering of M8040A High-performance BERT 64 Gbaud                                                                                                                                            | . 49 |

| Related Keysight Literature                                                                                                                                                                  | . 52 |

| Confidently Covered by Keysight Services                                                                                                                                                     | . 53 |

#### Introduction

The Keysight Technologies Inc. M8040A is a highly integrated BERT for physical layer characterization and compliance testing.

With support for pulse amplitude modulation 4-level, 3-level (PAM4, PAM3) and non-return-to-zero (NRZ) signals, and symbol rates up to 64 Gbaud (corresponds to 128 Gbit/s) it can be used for testing devices designed for 400/ 200 GbE, 800G, OIF CEI-56G and CEI-112G, PCIe ® 64/32/16/8/5 GT/s, USB4 Version 2,0, USB 3.2, USB4, Thunderbolt™ 3 and Thunderbolt™ 4.

The M8040A BERT's true error analysis provides repeatable and accurate results, optimizing the performance margins of your devices.

#### Key features

- Data rates from 2 to 32 and 64 Gbaud

- PAM4, PAM3 and NRZ selectable from user interface

- Built-in 5 tap transmitter FFE with multiple presets to compensate loss

- Integrated and calibrated jitter injection: RJ, LF and HF PJ (multi-tone, sinusoidal), BUJ, clk/2 jitter, sRJ, rSSC, and SSC (spread spectrum clocking)

- Forward Error Correction (FEC) encoding and error insertion for testing DUTs with FEC decoder

- Two pattern generator channels per module to emulate aggressor lane

- Linearity tests with adjustable PAM4 and PAM3 levels

- Interactive link training 2.5/5/8/16/ 32/64 GT/s PCI Express®

- Interactive link training for USB 3.2, 5 Gb/s and 10 Gb/s, x1 and x2

- New SSC clock switch profile supported according to CTS V1.02

- SKP OS filtering for 2.5/5/8/16/32 64 GT/s PCI Express® and SKP OS filtering for USB 3.2

- PCIe pre-coder support

- USB4 Version 2.0 pre-coder and scrambler support

- ALIGN filtering for SATA 3G / 6G and SAS 3G / 6G/ 12G

- Short connections to the DUT with remote heads for the pattern generator

- True PAM4 error detection in real-time for low BER levels

- Built-in and adjustable equalization to re-open closed eyes

- Integrated clock recovery and control of external clock recovery units N1076A/B, N1077A, N1078A

- RI and SI level interference injection via M8054A interference source for M8194A/95A/96A AWG

- Graphical user interface and remote control via M8000 system software

- Error distribution analysis to debug burst error conditions, real-time

- Reference clock multiplier support with SSC extended to 64 Gbaud

#### **Applications**

The M8040A can be used for receiver (input) testing for many emerging interconnect standards, such as:

- IEEE 802.3bs 400 and 200 Gigabit Ethernet (200GAUI, 200GBASE, 400GAUI, 400GBASE)

- IEEE 802.3bj 100 Gigabit Ethernet

- IEEE 802.3cd 50, 100 and 200 Gigabit Ethernet

- IEEE 802.3ck 400 Gigabit Ethernet

- OIF CEI 56G and -112G (NRZ and PAM4 versions)

- 25G and 50G PON

- PCI Express 64/32/16/8/5/2.5 GT/s

- CCIX

- SAS

- USB 3.2, USB4 and USB4 Version 2.0

- Thunderbolt 3/4

- DisplayPort 2.1

- MIPI M-PHY Gear 5

- 64G/112G Fiber Channel

- InfiniBand-HDR and NDR

- Proprietary interfaces for chip-to-chip, chip-to-module, backplanes, repeaters, and active optical cables, operating up to 64 Gbaud.

#### M8000 Series of BER Test solutions

Simplified time-efficient testing is essential when you are developing next-generation computer, consumer, or communication devices

The Keysight M8000 Series is a highly integrated BER test solution for physical layer characterization, validation, and compliance testing.

With support for a wide range of data rates and standards, the M8000 Series provides accurate, reliable results that accelerate your insight into the performance margins of high-speed digital devices.

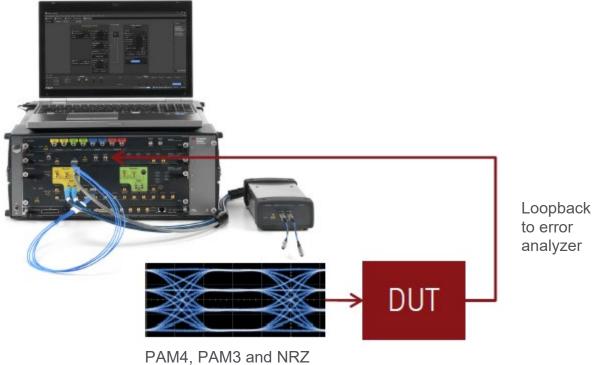

Figure 1. The M8000 Series BER test solution is highly integrated and scalable to address the test challenges of the next generation of high-speed digital receiver test.

The M8040A high-performance BERT 64 Gbaud extends the M8000 Series for 400G data center interconnect testing and PCIe 4/5, CCIX, SAS, USB 3.2, USB4 and TBT3/4 receiver characterization.

## M8040A High-performance BERT 64 Gbaud

Simplifies accurate receiver characterization of devices operating up to 32 and 64 Gbaud with NRZ, PAM3 and PAM4 signals

#### Highest level of integration streamlines receiver test setups

With the M8040A, all critical test capabilities for input/receiver (RX) characterization are built in. The pattern generator module provides calibrated and integrated jitter sources and de-emphasis to emulate the transmitter (TX) and to compensate for channel loss in the test setup. In addition, the M8040A provides an internal clock synthesizer and a second pattern generator output channel to emulate an aggressor lane.

The analyzer provides true PAM4 and NRZ error analysis in real time and full sampling to measure down to very low BER and SER.

This high level of integration with the M8040A makes the receiver test set-up connections easier and more robust. Setup and debug time are shortened, calibration is simpler, and the frequency of re-adjustments is reduced, resulting in a more efficient use of overall test time.

1 and 2 channel pattern generator

With remote heads, de-emphasis and jitter

Figure 2. The M8040A streamlines complex receiver test setups. Each of the 1 or 2 pattern generator channels provides built-in de-emphasis, jitter sources, and a remote head to reduce the distance between the generator output and the DUT test board. The full sampling error analyzer can detect errors in real-time for NRZ, PAM3 and PAM4 signals without the need to split up the PAM4 signal for multiple error detector channels

#### Repeatable and Accurate Results with M8040A

The M8040A high-performance BERT provides clean NRZ, PAM3 and PAM4 signals up to 64 Gbaud with fast transitions and low intrinsic jitter. The remote head concept of M8040A with the short 1.85 mm cables brings the performance close to the device under test, minimizing signal degradations caused by lossy channels.

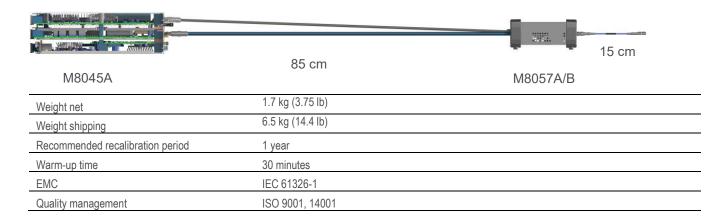

Figure 3. The remote head M8057A/B is required for each channel and is required for NRZ, PAM3 and PAM4 signals. It contains an adjustable gain amplifier without re-timer. Users can select NRZ, PAM3 or PAM4 coding and de-emphasis taps settings from the user interface with no need to reconnect cables. The cable between the remote head and the module is 0.85 m long. This allows positioning the remote head closely to the test board for the device under test.

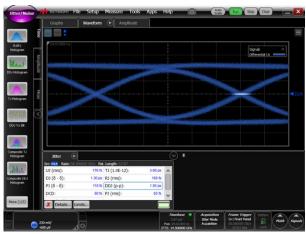

Figure 5. Clean 58 Gbaud NRZ output signal of pattern generator module M8045A with remote head M8057B using the internal clock source with 600 mV output amplitude and PRBS 2<sup>15</sup>-1. Measured with Infiniium DCA-X 86100D with N1045A and manual de-emphasis adjustment.

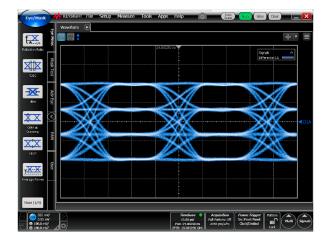

Figure 4. Clean 26.5625 Gbaud PAM4 output signal of pattern generator module M8045A with remote head M8057B using the internal clock source with 600 mV output amplitude and PRBS 2<sup>15</sup>-1. Measured with Infiniium DCA-X 86100D and N1045A and manual de-emphasis adjustment.

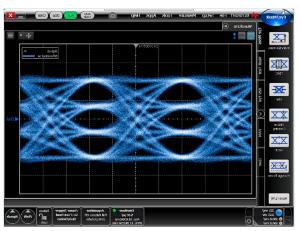

Figure 6. Clean 53.125 Gbaud PAM4 output signal of pattern generator module M8045A with remote head M8057B using the internal clock source with 600 mV output amplitude and PRBS 2<sup>15</sup>-1. Measured with Infiniium DCA-X 86100D and N1045A and manual de-emphasis adjustment.

#### Emulate Stress Conditions for NRZ, PAM3 and PAM4 Input Tolerance Testing with M8040A

M8040A provides all capabilities required for input tolerance test:

- 1 or 2 channels. Second channel can be used as aggressor lane to emulate crosstalk effects

- Data rates are adjustable from 2 Gb/s NRZ up to 64 Gbaud PAM3 or PAM4, selectable NRZ or PAM4 or PAM3

- Algorithmic PRBS, QPRBS, PRTS and memory-based patterns, pattern sequencer with loops, error injection at the bit level (NRZ patterns) and at the symbol level (PAM3 and PAM4 patterns)

- Generates FEC encoded patterns with pre-coder on 1 lane to test DUTs with FEC decoder

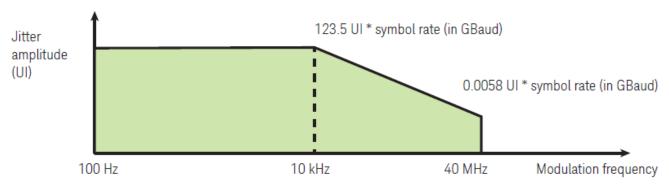

- Built-in and calibrated jitter sources that can be used simultaneously: random jitter (RJ), multi-UI low-frequency jitter, multi-tone high-frequency jitter, BUJ, clk/2 jitter, spread-spectrum clocking (SSC), residual SSC (rSSC), spectrally distributed RJ (sRJ)

- Lock system clock to an external reference clock with a multiplying PLL

- De-emphasis for pre- and post-cursor to emulate transmitter de-emphasis and compensate for loss in the test setup

- Inject random interference (RI) and sinusoidal interference (SI) by couplers. The M8000 software controls M8054A, AWG M8195A and M8196A as RI/SI source or as aggressor lanes

- Automated jitter tolerance testing

|                     | NRZ        | PAM4                        |  |

|---------------------|------------|-----------------------------|--|

|                     |            | $\mathcal{L}_{\mathcal{M}}$ |  |

| Effective data rate | Bit rate   | Symbol rate                 |  |

| 32 Gbit/s           | 32 Gbit/s  | 16 Gbaud                    |  |

| 64 Gbit/s           | 64 Gbit/s  | 32 Gbaud                    |  |

| 128 Gbit/s          | 128 Gbit/s | 64 Gbaud                    |  |

Covered by M8040A

| Related IEEE802.3cd<br>50/100/200GBASE/GAUI proposed<br>symbol rate * # of lanes | Related IEEE802.3bs<br>200GBASE/200GAUI<br>symbol rate # of lanes | Related IEEE802.3bs<br>400GBASE/400GAUI<br>symbol rate # of lanes | Related OIF rates                                                                             | CEI-56G symbol                                                                                                                                               |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25. 78125 Gb/s Gb/s NRZ * 1 lane                                                 | 26.5625 Gbit/s NRZ * 8 lanes                                      | 26.5625 Gbit/s NRZ * 16 lanes                                     |                                                                                               |                                                                                                                                                              |

| 26.5625 Gbaud PAM4 *1/2/4 lanes 53.125 Gbaud PAM4 *1/2 lanes                     | 26.5625 Gbaud PAM4 * 4 lanes                                      | 26.5625 Gbaud PAM4 * 8 lanes<br>53.125 Gbit/s NRZ * 8 lanes       | LR-PAM4:<br>MR-PAM4:<br>MR-NRZ:<br>VSR-PAM4:<br>VSR-NRZ:<br>XSR-PAM4:<br>XSR-NRZ:<br>USR-NRZ: | 19.6 to 30 Gbaud<br>18 to 29 Gbaud<br>39 to 56.2 Gbit/s<br>18 to 29 Gbaud<br>39 to 56.2 Gbit/s<br>18 to 29 Gbaud<br>39.8 to 58 Gbit/s<br>19.6 to 58.0 Gbit/s |

Figure 7.M8040A supports data rates up to 32 Gb/s NRZ, 64 Gb/s NRZ, 32 Gbaud PAM4 and 64 Gbaud PAM4. The user interface allows selection of NRZ and PAM4 without reconnecting the BERT test setup.

#### Master PAM4 Receiver Test Challenges with M8040A

Design and test engineers who need to characterize devices that support PAM4 data formats are facing new test challenges in addition to the signal integrity issues known from 25 Gb/s NRZ device testing.

For PAM4 input receiver tolerance test, this means impairments that may occur in the real-world should be tolerated by the receiver under test without exceeding the desired BER level. Typical receiver tests include jitter tolerance, interference tolerance test and level sensitivity margins that are applicable for NRZ and PAM4 devices. In addition, PAM4 receivers require additional margin testing for level non-linearity, crosstalk effects from adjacent lanes and vertical eye closure.

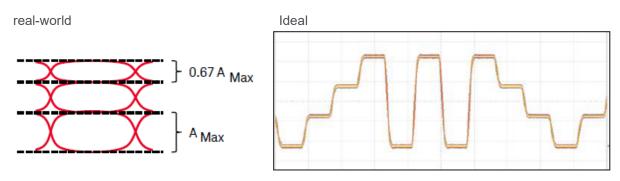

Figure 8. PAM4 eyes can show a level separation mismatch. Receivers must be able to detect the digital signal content properly within the given mismatch ratio.

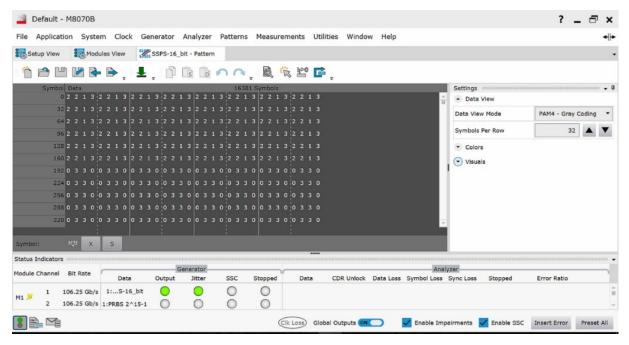

#### Real-time Error Analysis for PAM4, PAM3 and NRZ Signals

Receiver verification checks if the receiver under test operates below the specified BER while emulating the worst-case transmitter and channel conditions. BER measurements are well established for NRZ signals by using a traditional BERT, but what does this mean for PAM4 signals?

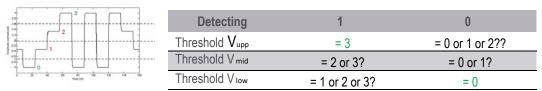

For proper error detection of PAM4 signals, all thresholds (V<sub>low</sub>, V<sub>mid</sub>, and V<sub>upper</sub>) have to be analyzed simultaneously to ensure a correct symbol error measurement (see Figure 9). If a "1" is detected at the V<sub>mid</sub> threshold, the received pattern can have level 2 or 3. Only if the level detected at V<sub>upp</sub> is checked simultaneously with V<sub>mid</sub>, it can be determined if the received inputs have the correct level for a 2 or a 3. If two thresholds are errored within one UI, this case translates just into one symbol error.

| PAM-4 | Vupp | Vmid | Vlow | Gr | ay |

|-------|------|------|------|----|----|

| 3     | 1    | 1    | 1    | 1  | 0  |

| 2     | 0    | 1    | 1    | 1  | 1  |

| 1     | 0    | 0    | 1    | 0  | 1  |

| 0     | 0    | 0    | 0    | 0  | 0  |

Figure 9. Only a true PAM4 error analyzer like M8040A, can provide a PAM4 symbol error rate in real-time without post-processing. Error ratios down to  $10^{-15}$  or error-free can be measured even for long PRBS 2  $^{31}$ –1, SSPRQ, QPRBS13-CEI or QPRBS31-CEI patterns. Errored 0,1,2,3 and symbol errors can be counted separately for further debugging.

- The M8040A provides real-time error analysis of PAM4, PAM3 and NRZ signals.

- Key capabilities of the error analyzer module M8046A include:

- One differential channel per analyzer module

- Symbol rates from 5 to 58 Gbaud for PAM4 and PAM3 and from 5 to 64 Gb/s for NRZ

- Native PAM4 decoding

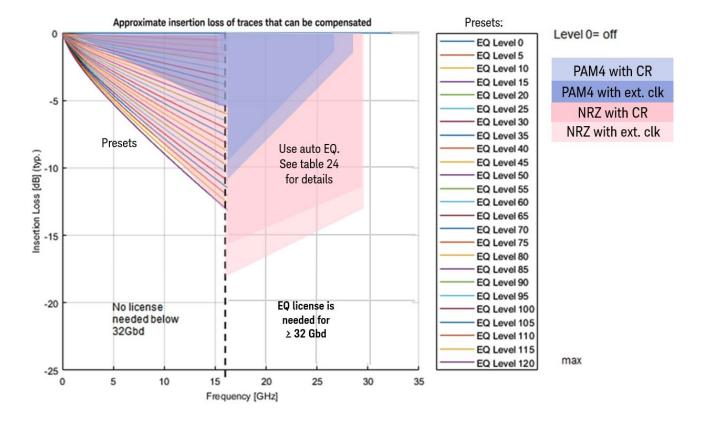

- Built-in equalization to re-open closed eyes at the analyzer input

- Selectable expected patterns like QPRBS31, SSPRQ, pattern memory, pattern sequencing, masking, Gray coding and custom PAM4 symbol mapping

- Integrated clock recovery option and control via M8070ADVB of external clock recovery units N1076A/B, N1077A, N1078A

- DUT control interface allows to access built-error counters from the M8070ADVB advanced measurement software package.

- Can be used in combination with M8045A pattern generator or AWGs M8195/6/4A

## Automated Receiver Calibration and Characterization for IEE 802.3bs/cd, IEEE 802.3ck, OIF-CEI-56G-VSR/-MR/-LR-PAM4, PCI Express 4.0, 5.0 and 6.0, USB 3.2, USB4 Version 2.0,TBT3 and TBT4 Interfaces

To simplify the compliance testing and characterization of receiver test, Keysight provides automated receiver test automation software for various electrical and optical interface standards. Here is an overview of test automation software solutions available supporting the M8040A high-performance BERT.

| Standard              | Interface                                                    | Variants                                                                       | BERT   | Test Automation Software                                                                                                                                                                           |

|-----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE<br>802.3bs/ cd   | Electrical,<br>Chip-to-module,<br>Chip-to-chip,<br>Backplane | 400GAUI-8<br>200GAUI-4                                                         | M8040A | M8091BSCA Electrical Receiver Conformance Test<br>Application for IEEE 802.3bs/ cd                                                                                                                 |

| IEEE<br>802.3bs/cd/db | Optical                                                      | 400GBASE-LR8/-FR8<br>and 200GBASE-LR4/-FR4/-DR4<br>400G-DR4/-FR4/-SR4 and MSAs | M8040A | N4917BSCB Optical Receiver Stress Test Solution                                                                                                                                                    |

| IEEE 802.3ba          | Optical                                                      | 100GBASE-SR4/LR4/ER4 and MSAs                                                  | M8040A | N4917BACA Optical Receiver Stress Test Solution                                                                                                                                                    |

| IEEE 802.3ck          | Electrical,<br>Chip-to-module,<br>Chip-to-chip,              | 100GAUI-1<br>400GAUI-4                                                         | M8040A | M8091CKCA Pre-compliance Receiver Test Automation for IEEE 802.3ck, draft 3.3                                                                                                                      |

| OIF CEI 4.0           | Electrical, host and module                                  | 56G-VSR,-MR, -LR PAM4                                                          | M8040A | M809256CA Electrical Receiver Conformance Test<br>Application for OIF-CEI-56G                                                                                                                      |

| PCI Express<br>4.0    | Electrical                                                   | PCIe 2.5/5/8/16 GT/s                                                           | M8040A | N5991PB4A Receiver Test Automation for PCIe 4.0 base specification N5991PC4A Receiver Test Automation for PCIe 4.0 PHY Test Specification for CEM N5991PA3A-ADD Automated LinkEQ RX and TX testing |

| PCI Express<br>5.0    | Electrical                                                   | PCIe 2.5/58/16/32 GT/s                                                         | M8040A | N5991PB5A Receiver Test Automation for PCIe 5.0 base specification N5991PC5A Receiver Test Automation for PCIe 5.0 PHY Test Specification for CEM N5991PA3A-ADD Automated LinkEQ RX and TX testing |

| PCI Express<br>6.0  | Electrical | PCIe 64 GT/s                               | M8040A | N5991PB6A Receiver Test Automation for PCIe 6.0 base specification – 64 GT/s only |

|---------------------|------------|--------------------------------------------|--------|-----------------------------------------------------------------------------------|

| SAS                 | Electrical | SAS 12 and 24 Gb/s                         | M8040A | N5991SA4A Receiver Test Automation for SAS                                        |

| SATA                | Electrical | SATA 3                                     | M8040A | N5991ST3A Receiver Test Automation for SATA                                       |

| CCIX                | Electrical | CCIX 20 and 25 GT/s                        | M8040A | N5991C25A Receiver Test Automation for CCIX                                       |

| USB 3.2             | Electrical | USB 3.2                                    | M8040A | N5991U32A Receiver Test Automation for USB 3.2                                    |

| USB4 Version<br>2.0 | Electrical | USB4 Gen2 (10G NRZ)<br>USB4 Gen3 (20G NRZ) | M8040A | N5991U42A Receiver Test Automation for USB4 Version 2.0                           |

|                     |            | USB4 Gen4 (25.6G PAM3)                     |        |                                                                                   |

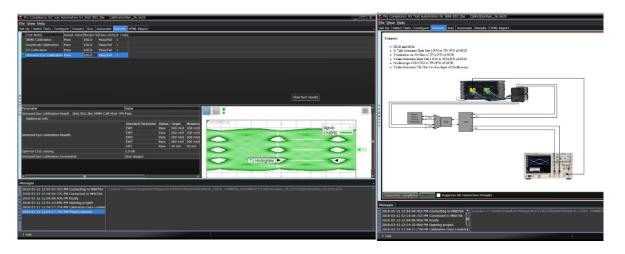

Figure 11. Automate the complicated stress signal calibration procedure with guided steps how to connect the test setup and pre-compliance measurements by using the M8091CKCA receiver test automation software for IEEE 802.3bs for chip-to-module interfaces 400GAUI-8 and 200GAUI-4. The figure shows screen shots of the automation software with the results of a successful stress calibration (left side) and guided test setup (right side).

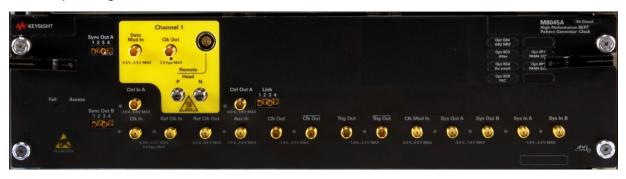

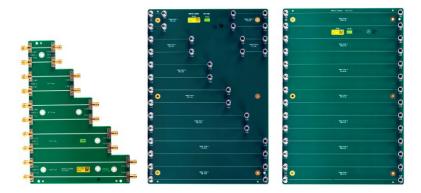

#### Specifications for M8045A and M8046A Modules and M8057A/B Remote Head

M8045A pattern generator module for two data channels, 3-slot AXIe

M8045A pattern generator module for one data channel, 3-slot AXIe

M8057A/B remote head with cable connections (0.85 m) front and rear view

M8046A analyzer module, 1-sot AXIe

Figure 12. Front panel views of pattern generator module M8045A (top) as 2 and 1 channel (center) versions, remote head M8057A/B, and error analyzer module M8046A (bottom). To allow a very short connection to the device under test, the remote head is used. One remote head is needed for each of the pattern generator data outputs of M8045A.

#### Specifications for Pattern Generator Module M8045A and Remote Head M8057A/B

The pattern generator supports symbol rates up to 32 Gbaud or 64 Gbaud, default is one channel and NRZ format.

The remote head M8057A/B is needed once per channel. Using the P and N outputs of the M8045A without remote head is prohibited.

For the following generator functions a separate module option is required:

- PAM4 coding up to 32 Gbaud (M8045A Option 0P3)

- PAM4 extension to 64 Gbaud (M8045A Option 0P6)

- Second data channel (M8045A Option 0G2)

- Advanced jitter sources (M8045A Option 0G3)

- De-emphasis (M8045A Option 0G4)

- Reference clock multiplier with bandwidth 2/5 MHz (M8045A Option 0G6)

- Forward Error Correction (FEC) encoding (M8045A Option 0G9)

#### Data output (DATA OUT 1, DATA OUT 2)

Table 1. Data output characteristics for M8045A with remote head M8057A/B.

| All timing parameters rea measured @ 0. | 5 V into ground at data outputs of remote head M8057A/B                                         |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|

| Symbol rate                             | 2.025 to 32.4 Gbaud for M8045A Option -G32                                                      |

|                                         | 2.025 to 58.0 Gbaud (all specifications are valid up to 58 Gbaud with over-programming up to    |

|                                         | 64.8 Gbaud) for M8045A Option -G64                                                              |

| Data format                             | NRZ (default)                                                                                   |

|                                         | PAM4 (requires M8045A Option -0P3 and for symbol rates above 32 Gbaud -0P6 in addition)         |

|                                         | PAM3 (requires M8045A Option -0P3)                                                              |

| Channels per module                     | 1 or 2 (requires M8045A Option -0G2 and second remote head)                                     |

| Amplitude with M8057B                   |                                                                                                 |

| for symbol rates < 58 Gbaud             | 80 mV to 0.9 Vpp single ended                                                                   |

|                                         | 160 mV to 1.8 Vpp differential                                                                  |

| Amplitude with M8057A                   | ··· ··· · · · · · · · · · · · · ·                                                               |

| For symbol rates < 32.4 Gbaud           | 50 mV to 0.9 Vpp single ended                                                                   |

|                                         | 100 mV to 1.8 Vpp differential                                                                  |

| For symbol rates < 58 Gbaud             | 50 mV to 0.6 Vpp single ended                                                                   |

|                                         | 100 mV to 1.2 Vpp differential                                                                  |

| Amplitude accuracy                      | ±10% ±10 mV typical (AC) <sup>1</sup>                                                           |

| Output voltage window                   | −1 to +3.0 V depends on external termination voltage <sup>5</sup>                               |

| External termination voltage            | –1 to +3.0 V                                                                                    |

| Offset accuracy                         | 25 mV +10% of offset +1% of amplitude. The offset is defined as 0.5 * (HIL+LOL). See $^{\rm 5}$ |

| Transition time <sup>2</sup>            | 9 ps typical (20 to 80%) for symbol rates > 32.4 Gbaud                                          |

|                                         | 11 ps typical (20% to 80%) for symbol rates ≤ 32.4 Gbaud                                        |

| Intrinsic total jitter                  | 8 ps typical @ 32.0 Gb/s NRZ, PRBS 15, BER 10 <sup>-12</sup>                                    |

| Intrinsic random jitter (NRZ)           | 5 mUl rms typical @ symbol rates between 2.025 Gbaud and < 22 Gbaud                             |

|                                         | 7 mUl rms typical @ symbol rates between 22 Gbaud and < 32.4 Gbaud                              |

|                                         | 10 mUl rms typical @ symbol rates between 32.4 Gbaud and < 40 Gbaud                             |

|                                         | 12 mUl rms typical @ symbol rates between 40 Gbaud and < 52 Gbaud                               |

|                                         | 10 mUI rms typical @symbol rates between 52 Gbaud and < 58 Gbaud                                |

|                                         | For M8045A with option -0G8 only:                                                               |

|                                         | 10 mUl rms typical @symbol rates between 49.5 Gbaud and < 58 Gbaud                              |

Table 1. Data output characteristics for M8045A with remote head M8057A/B. (continued)

| Data delay range                                   | 0 to 10 ns, resolution 100 fs                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data delay accuracy                                | ± (max. (1.5 ps or 10 mUI whatever is higher) + 1% of entered value) typical <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Electrical idle                                    | The output transitions from full swing to 0 V amplitude and vice versa at constant offset within 1 UI.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Skew between normal and complement output          | 3 ps maximum at the end of the recommended cable pair. Fixed.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Skew between data output ch 1 and data output ch 2 | 370 ps maximum <sup>4</sup> Repeatability after manual de-skew ± 300 ps typical                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Termination impedance range                        | To protect the output stage, the output is disabled when an unexpected voltage or termination impedance is detected.   DC output coupling mode:   Termination range for devices connected to data out:   • Unbalanced 50 $\Omega$ +15 $\Omega$ / -10 $\Omega$ • Typical balanced 100 $\Omega$ ±30 $\Omega$ typical   Operation into open <sup>7</sup> is possible for following ranges when DC coupled and balanced termination modes are selected:   • Output amplitude max. 450 mV   • Offset 0 to 370 mV |

| Termination modes                                  | Balanced/ unbalanced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Coupling                                           | DC/ AC selectable coupling of device under test                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Connectors                                         | 1.85 mm, female                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

- 1. At 5 Gbaud measured with DCA-X N1045A and clock pattern and in the middle of the eye

- 2. Measured with DCA-X N1045A

- 3. At constant temperature

- 4. Requires M8070A software revision 4.5 or M8070B SW 6.0 or later and a module serial number above DE56C00400

- 5. High level voltage range= 2/3\* Vterm 0.95 V < HIL < Vterm + 2 V

- 6. Low level voltage range= 2/3 \* Vterm 1 V < LOL < Vterm + 1.95 V

- 7. Available with M8070B SW 7.5 and higher

## De-emphasis (DATA OUT)

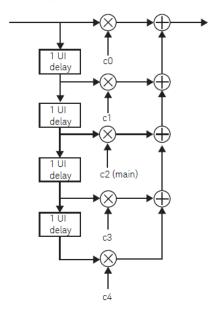

The M8045A provides built-in de-emphasis with positive and negative cursors based on a finite impulse response (FIR) filter see figure 11. Users can enter the de-emphasis in coefficient values. The M8045A supports five de-emphasis cursors with an adjustable main-cursor position between cursor 1 and cursor 3. Pre-requisite to use the adjustable main cursor is M8070B software revision 7.1 or later. This allows selecting the following configuration

| Main cursor position Number of pre-cursors |   | Number of post-cursors |

|--------------------------------------------|---|------------------------|

| 1                                          | 1 | 3                      |

| 2                                          | 2 | 2                      |

| 3                                          | 3 | 1                      |

Table 2. Specifications for multi-tap de-emphasis (requires Option 0G4).

|                               | NRZ                                                                   | PAM4                                                |  |  |

|-------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|--|--|

| De-emphasis taps              | 5, can be adjusted for each channel independently                     | 5, can be adjusted for each channel independently   |  |  |

| Coefficient c0                | $0.0 \text{ to } \pm 0.40^{\text{ 1}}$                                | $0.0 \text{ to } \pm 0.40^{\text{ 1}}$              |  |  |

| Coefficient c1                | $0.0 \text{ to } \pm 0.40^{\text{ 1}}$                                | $0.0 \text{ to } \pm 0.40^{-1}$                     |  |  |

| Coefficient c2                | $0.0 \text{ to } \pm 1.0^{\text{ 1}}$                                 | $0.0 \text{ to } \pm 1.0^{\text{ 1}}$               |  |  |

| Coefficient c3                | $0.0 \text{ to } \pm 0.40^{\text{ 1}}$                                | $0.0 \text{ to } \pm 0.40^{-1}$                     |  |  |

| Coefficient c4 <sup>2</sup>   | $0.0 \text{ to } \pm 0.40^{\text{ 1}}$                                | $0.0 \text{ to } \pm 0.40^{\text{ 1}}$              |  |  |

| Cursor coefficient resolution | 0.001 is supported in user interface with SW 9.0 or                   | 0.001 is supported in user interface with SW 9.0 or |  |  |

|                               | later, hardware resolution is more coarse.                            | later, hardware resolution is more coarse.          |  |  |

| Tap optimization              | Auto-optimization of DE taps is possible when using DCA and M8070ADVB |                                                     |  |  |

- 1. Sum of all cursors absolute values may not exceed 1.0 lc0l+lc1l+lc2l+lc3l+lc4l ≤ 1. Also, lc0l, lc1l, lc3l, lc4l < lc2l\_

- 2. Requires M8070A software 5.0 or M8070B SW 6.0 or later.

Figure 13. The pattern generator of M8045A provides integrated de-emphasis to emulate TX equalization. The example shows a configuration with two post-cursors c3 and c4, the main cursor c2 and two pre-cursors c0 and c1.

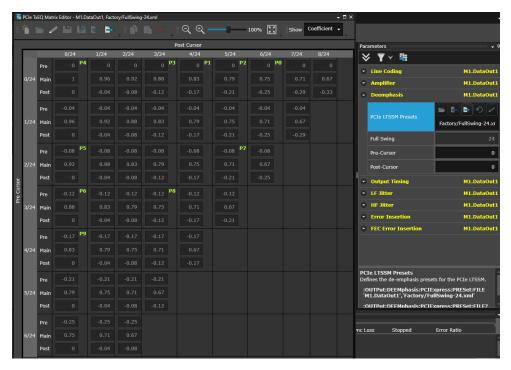

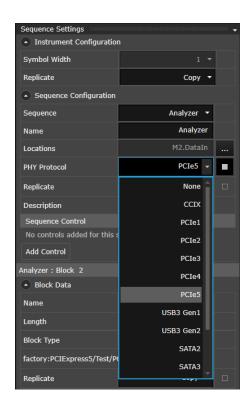

#### De-emphasis presets for PCIe testing

If PHY protocol mode PCle3, PCle4, PCle5, PCle6 for the pattern generator sequence is selected the deemphasis capabilities are switched from the multi-tap FIR to a PCI Express type of FIR editor with coefficient entry as integers dependent of the selected full swing. A full swing from 24 to 63 coefficient resolution steps can be selected.

Figure 14. The TxEQ matrix editor can be accessed if the PHY protocol mode PCle 3, PCle 4 or PCle 5 is selected for the pattern generator sequence.

#### Forward Error Correction (FEC) encoding (DATA OUT)

The M8045A pattern generator module supports forward error correction (FEC) and precoding encoding according to IEEE802.3cd.

Users can inject pre- and post-FEC errors to test the DUT's devices FEC decoder function.

Table 3. Specifications for FEC (Forward Error Correction) encoding (requires M8045A Option 0G9).

| FEC encoding                 | 50GBASE-R, 100GBASE-R, 200GBASE-R, 400GBASE-R                                                                                                                                                                                                         |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reed-Solomon Code            | RS (544,514)                                                                                                                                                                                                                                          |

| Scrambler                    | PRBS 2 <sup>58</sup> -1                                                                                                                                                                                                                               |

| Pattern sequence             | These patterns form pattern library can be FEC encoded: Remote faults, Scrambled idle                                                                                                                                                                 |

| Line coding                  | PAM4                                                                                                                                                                                                                                                  |

| Symbol rate                  | 26.5625 GBd PAM4: 50GBASE (all PCS lanes), 100GBASE (PCS 0-9 on Channel 1 and 10-19 on Channel 2), 200GBASE (PCS 0,1) 400GBASE (PCS 01,) 53.125 Gbd PAM4: 100GBASE (all PCS lanes), 400GBASE (PCS 0,1, 2,3 on Channel 1 and PCS 4,5,6,7 on Channel 2) |

| FEC symbol error injection   | For 50GBASE-R: Pre-FEC: insertion of a single BIP Post-FEC: FEC symbol errors, randomly distributed, selectable amount of symbol errors per FEC frame                                                                                                 |

| Pre-coder                    | PAM4: 1/ (1+D) mod4, can be switched on/off. Follows IEEE802.3 Clause 135.5.7.2. for PAM4 encoded lanes.                                                                                                                                              |

| Synchronization to A400GE-DD | Yes, requires trigger and reference clock connection. Requires M8045A-0G9 and M8070B                                                                                                                                                                  |

| and G800GE                   | 7.0 or later.                                                                                                                                                                                                                                         |

| Pre-requisites               | M8045A with option 0P3 and 0G9, M8070A SW 5.1/ M8070B 6.7 or later.                                                                                                                                                                                   |

#### Clock output 1 and 2 (Channel 1 CLK OUT, channel 2 CLK OUT)

These clock output provide two modes. They can operate with the same jitter as the corresponding data output or operate in a clean mode.

Table 4. Specifications for channel 1 clock output and channel 2 clock output.

| FEC encoding                                                                                |     | 1.0125 to 16.2 GHz with M8045A-G32                                                               |

|---------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------|

|                                                                                             |     | 1.0125 to 32.4 GHz with M8045A-G64                                                               |

| Frequency divider fact                                                                      | ors | Symbol rate / clock divider: 2, 4, 8, 16. Divided output frequency must fit into frequency range |

| Clean clock mode                                                                            | On  | No jitter injection, no SSC                                                                      |

|                                                                                             | Off | Same jitter and SSC as data output of same channel                                               |

| Amplitude                                                                                   |     | 1 V typical nominal single ended                                                                 |

| Duty cycle                                                                                  |     | 50%, accuracy ± 15% typical                                                                      |

| Intrinsic random jitter                                                                     |     | 6 mUI rms typical for symbol rates between 2.025 Gbaud and ≤ 27 Gbaud                            |

|                                                                                             |     | 10 mUI rms typical for symbol rates > 27 Gbaud.                                                  |

|                                                                                             |     | Refers to mUI of symbol rate.                                                                    |

| Termination 50 $\Omega$ into GND or external termination voltage. Do not operate into open. |     | $50~\Omega$ into GND or external termination voltage. Do not operate into open.                  |

| Coupling AC coupled. Single ended.                                                          |     | AC coupled. Single ended.                                                                        |

| Connectors                                                                                  |     | 3.5 mm, female                                                                                   |

#### Clock output (CLK OUT)

This is a differential clock output with many sub-rate clock dividers. LF SJ and HF jitter can be turned off and on individually. HF jitter has the same setting as HF jitter of data output of channel 1. Delay on the trigger output also impacts clock output.

Table 5. Clock output specifications.

| CLK frequency range   CLK frequency range   T (1, 2, 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   T (1 < 4, 8, 10, 16, 20, 24, 24, 24, 24, 24, 24, 24, 24, 24, 24                                                  |                                     |       |                                                                                                                                                                                                                                                                                                                                      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clock divider in relation to clock frequency range   n* (1, 2, 4, 8, 10, 16, 20, 24, 30, 32, 40, 50, 64, 66, 80) with   n = 1 < 16.2 GHz   n = 2 for 16.2 GHz   to 32.4 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLK frequency range                 |       | 2.025 to 16.20 GHz                                                                                                                                                                                                                                                                                                                   |  |  |

| Frequency resolution 1 Hz  Frequency accuracy ± 15 ppm  Amplitude Differential Single ended 0.1 to 1 V, 5 mV steps 0.1 to 1 V, 5 mV steps  Output voltage window −1 to +3 V  External termination voltage −1 to +3 V  Transition times 20 ps typical (20 to 80%)  Duty cycle 50%, accuracy ± 15%  Clock modes See Table 6  Intrinsic random jitter 300 fs rms typical at 16.2 GHz and clock divider = 1  LF Jitter:  Can be set independently from Data Out  Has the same LF jitter parameters and ranges as Data Out  HF Jitter:  On → the jitter values from Data Out 1 HF Jitter are applied to Clock Out  Off → no HF Jitter  SSC:  SSC is a system-wide parameter and therefore applies to CLK OUT too  Jitter delay: from + 40 ns to -40 ns  SSB phase noise² −80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz  Termination 50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage  Coupling DC coupled, differential                                                                                                                                                                                                                                                                                                                                                                                 |                                     |       | n= 1 < 16.2 GHz<br>n= 2 for 16.2 GHz to 32.4 GHz                                                                                                                                                                                                                                                                                     |  |  |

| Frequency accuracy ± 15 ppm  Amplitude Differential 0.2 to 2.0 V, 10 mV steps Output voltage window -1 to +3 V 1  External termination voltage -1 to +3 V 50%, accuracy ± 15%  Clock modes See Table 6  Intrinsic random jitter 300 fs rms typical at 16.2 GHz and clock divider = 1  LF Jitter:  Can be set independently from Data Out HF Jitter reameters and ranges as Data Out HF Jitter:  On -> the jitter values from Data Out1 HF Jitter are applied to Clock Out Off -> no HF Jitter  SSC:  SSC is a system-wide parameter and therefore applies to CLK OUT too Jitter delay: from + 40 ns to -40 ns  SSB phase noise² -85 dBc/Hz typical with 10 kHz offset and internal clock and 10/100 MHz as external reference cloc -80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz  Termination DC coupled, differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |       | For other dividers use TRIG OUT                                                                                                                                                                                                                                                                                                      |  |  |

| Amplitude Differential Single ended 0.2 to 2.0 V, 10 mV steps 0.1 to 1 V, 5 mV steps  Output voltage window1 to +3 V 1  External termination voltage -1 to +3 V 1  Transition times 20 ps typical (20 to 80%)  Duty cycle 50%, accuracy ± 15%  Clock modes See Table 6  Intrinsic random jitter 300 fs rms typical at 16.2 GHz and clock divider = 1  LF Jitter:  Can be set independently from Data Out  Has the same LF jitter parameters and ranges as Data Out  HF Jitter:  On -> the jitter values from Data Out1 HF Jitter are applied to Clock Out  Off -> no HF Jitter  SSC:  SSC is a system-wide parameter and therefore applies to CLK OUT too  Jitter delay: from + 40 ns to -40 ns  SSB phase noise² -85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock —80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz  Termination 50 \( \Omega \text{ intermination voltage} \)  DC coupling \( \Omega \text{ DC coupled, differential} \)                                                                                                                                                                                                                                                                                                                                                                                              | Frequency resolu                    | ıtion | 1 Hz                                                                                                                                                                                                                                                                                                                                 |  |  |

| Single ended       0.1 to 1 V, 5 mV steps         Output voltage window       -1 to +3 V 1         External termination voltage       -1 to +3 V         Transition times       20 ps typical (20 to 80%)         Duty cycle       50%, accuracy ± 15%         Clock modes       See Table 6         Intrinsic random jitter       300 fs rms typical at 16.2 GHz and clock divider = 1         Jitter injection         LF Jitter:       • Can be set independently from Data Out         • Has the same LF jitter parameters and ranges as Data Out         HF Jitter:       • On -> the jitter values from Data Out 1 HF Jitter are applied to Clock Out         • Off -> no HF Jitter       SSC:         • SSC is a system-wide parameter and therefore applies to CLK OUT too         Jitter delay: from + 40 ns to -40 ns         SSB phase noise²       -85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock and dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz         Termination       50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage         Coupling       DC coupled, differential                                                                                                                                                         | Frequency accura                    | acy   | ± 15 ppm                                                                                                                                                                                                                                                                                                                             |  |  |

| External termination voltage       -1 to +3 V         Transition times       20 ps typical (20 to 80%)         Duty cycle       50%, accuracy ± 15%         Clock modes       See Table 6         Intrinsic random jitter       300 fs rms typical at 16.2 GHz and clock divider = 1         Jitter injection       LF Jitter: <ul> <li>Can be set independently from Data Out</li> <li>Has the same LF jitter parameters and ranges as Data Out</li> <li>HF Jitter:             <ul> <li>On -&gt; the jitter values from Data Out1 HF Jitter are applied to Clock Out</li> <li>Off -&gt; no HF Jitter</li> <li>SSC:</li> <li>SSC is a system-wide parameter and therefore applies to CLK OUT too</li> <li>Jitter delay: from + 40 ns</li> <li>SSB phase noise²</li> <li>-85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock and dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz</li> <li>Termination</li> <li>50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage</li> <li>Coupling</li> <li>DC coupled, differential</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li> <li>Termination</li></ul></li></ul> | 7                                   |       |                                                                                                                                                                                                                                                                                                                                      |  |  |

| Transition times  20 ps typical (20 to 80%)  Duty cycle  50%, accuracy ± 15%  Clock modes  See Table 6  Intrinsic random jitter  300 fs rms typical at 16.2 GHz and clock divider = 1  LF Jitter:  • Can be set independently from Data Out  • Has the same LF jitter parameters and ranges as Data Out  HF Jitter:  • On -> the jitter values from Data Out1 HF Jitter are applied to Clock Out  • Off -> no HF Jitter  SSC:  • SSC is a system-wide parameter and therefore applies to CLK OUT too  Jitter delay: from + 40 ns to -40 ns  SSB phase noise²  -85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock  -80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz  Termination  50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage  Coupling  DC coupled, differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output voltage wi                   | indow | -1 to +3 V <sup>1</sup>                                                                                                                                                                                                                                                                                                              |  |  |

| Duty cycle       50%, accuracy ± 15%         Clock modes       See Table 6         Intrinsic random jitter       300 fs rms typical at 16.2 GHz and clock divider = 1         Jitter injection       LF Jitter: <ul> <li>Can be set independently from Data Out</li> <li>Has the same LF jitter parameters and ranges as Data Out</li> <li>HF Jitter:                 <ul> <li>On -&gt; the jitter values from Data Out1 HF Jitter are applied to Clock Out</li> <li>Off -&gt; no HF Jitter</li> <li>SSC:</li> <li>SSC is a system-wide parameter and therefore applies to CLK OUT too</li> <li>Jitter delay: from + 40 ns to -40 ns</li> <li>SSB phase noise²</li> <li>- 85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock – 80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz</li> <li>Termination</li> <li>50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                      |                                     |       | -1 to +3 V                                                                                                                                                                                                                                                                                                                           |  |  |

| Clock modes       See Table 6         Intrinsic random jitter       300 fs rms typical at 16.2 GHz and clock divider = 1         Jitter injection         LF Jitter:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Transition times                    |       | 20 ps typical (20 to 80%)                                                                                                                                                                                                                                                                                                            |  |  |

| Ditter injection   LF Jitter:   Can be set independently from Data Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Duty cycle                          |       | 50%, accuracy ± 15%                                                                                                                                                                                                                                                                                                                  |  |  |

| LF Jitter:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock modes                         |       | See Table 6                                                                                                                                                                                                                                                                                                                          |  |  |

| <ul> <li>Can be set independently from Data Out</li> <li>Has the same LF jitter parameters and ranges as Data Out</li> <li>HF Jitter:         <ul> <li>On -&gt; the jitter values from Data Out1 HF Jitter are applied to Clock Out</li> <li>Off -&gt; no HF Jitter</li> </ul> </li> <li>SSC:         <ul> <li>SSC is a system-wide parameter and therefore applies to CLK OUT too</li> <li>Jitter delay: from + 40 ns to -40 ns</li> </ul> </li> <li>SSB phase noise<sup>2</sup> <ul> <li>- 85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock – 80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz</li> </ul> </li> <li>Termination</li> <li>50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage</li> <li>Coupling</li> <li>DC coupled, differential</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Intrinsic random jitter             |       | 300 fs rms typical at 16.2 GHz and clock divider = 1                                                                                                                                                                                                                                                                                 |  |  |

| - 80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz       Termination     50 Ω into GND or external termination voltage. Do not operate into open. Unused outputs must be terminated into termination voltage       Coupling     DC coupled, differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Jitter injection                    |       | <ul> <li>Can be set independently from Data Out</li> <li>Has the same LF jitter parameters and ranges as Data Out</li> <li>On -&gt; the jitter values from Data Out1 HF Jitter are applied to Clock Out</li> <li>Off -&gt; no HF Jitter</li> <li>SSC:</li> </ul> SSC is a system-wide parameter and therefore applies to CLK OUT too |  |  |

| terminated into termination voltage  Coupling DC coupled, differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SSB phase noise <sup>2</sup>        |       | <ul> <li>85 dBc/ Hz typical at 10 kHz offset and internal clock and 10/100 MHz as external reference clock</li> <li>80 dBc/Hz typical with 10 kHz offset for reference clock multiplier bandwidth 0.1 MHz</li> </ul>                                                                                                                 |  |  |

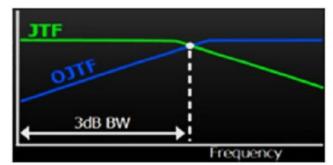

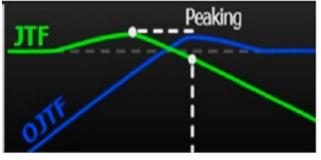

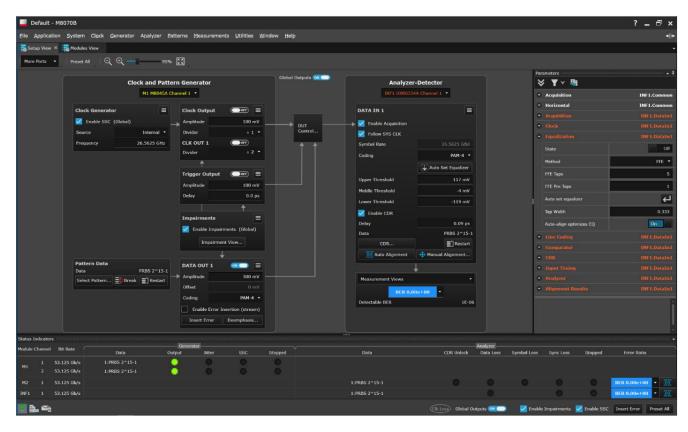

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | terminated into termination voltage |       | terminated into termination voltage                                                                                                                                                                                                                                                                                                  |  |  |